Systemarchitektur

Tensor Processing Units (TPUs) sind anwendungsspezifische integrierte Schaltungen (Application-Specific Integrated Circuits, ASICs), die von Google entwickelt wurden, um ML-Arbeitslasten zu beschleunigen. Cloud TPU ist ein Google Cloud-Dienst, der TPUs als skalierbare Ressource zur Verfügung stellt.

TPUs sind für die schnelle Ausführung von Matrixvorgängen konzipiert und somit ideal für ML-Arbeitslasten. Sie können ML-Arbeitslasten auf TPUs mit Frameworks wie TensorFlow, Pytorch und JAX ausführen.

Nutzungsbedingungen von Cloud TPU

Wenn Sie mit Cloud TPUs noch nicht vertraut sind, finden Sie weitere Informationen auf der Startseite der TPU-Dokumentation. In den folgenden Abschnitten werden die in diesem Dokument verwendeten Begriffe und verwandten Konzepte erläutert.

Batchinferenz

Als Batch- oder Offline-Inferenz wird eine Inferenz außerhalb von Produktionspipelines in der Regel für eine Vielzahl von Eingaben ausgeführt. Die Batchinferenz wird für Offlineaufgaben wie das Hinzufügen von Labels zu Daten und auch zum Bewerten des trainierten Modells verwendet. Latenz-SLOs haben keine Priorität für Batchinferenzen.

TPU-Chip

Ein TPU-Chip enthält einen oder mehrere TensorCores. Die Anzahl der TensorCores hängt von der Version des TPU-Chips ab. Jeder TensorCore besteht aus einer oder mehreren Matrixmultiplikationseinheiten (MXUs), einer Vektoreinheit und einer Skalareinheit.

Eine MXU besteht aus 128-x-128-Multiplikationsakkumulatoren in einem systolischen Array. MXUs liefern den Großteil der Rechenleistung in einem TensorCore. Jede MXU kann 16.000 Multiplikations- und Akkumulationsvorgänge pro Zyklus ausführen. Alle Multiplizierungen nehmen bfloat16-Eingaben, aber alle Akkumulationen werden im FP32-Zahlenformat ausgeführt.

Die Vektoreinheit wird für allgemeine Berechnungen wie Aktivierungen und Softmax verwendet. Die Skalareinheit wird zur Steuerung des Ablaufs, zur Berechnung von Speicheradressen und anderen Wartungsvorgängen verwendet.

TPU-Cube

Eine 4x4x4-Topologie. Dies gilt nur für 3D-Topologien, die mit der TPU-Version v4 beginnen.

Inferenz

Inferenz ist der Vorgang, bei dem mithilfe eines trainierten Modells Vorhersagen für neue Daten getroffen werden. Sie werden bei der Auslieferung verwendet.

Mehrere Segmente im Vergleich zu einem einzelnen Segment

Multislice ist eine Gruppe von Slices, die die TPU-Konnektivität über die ICI-Verbindungen (Inter-Chip Interconnect) hinaus erweitert und das Data Center Network (DCN) für die Übertragung von Daten über ein Slice hinaus nutzt. Die Daten in jedem Segment werden weiterhin über ICI übertragen. Mit dieser Hybridkonnektivität ermöglicht Multislice die Parallelität zwischen Segmenten und ermöglicht Ihnen, für einen einzelnen Job eine größere Anzahl von TPU-Kernen zu verwenden, als ein einzelnes Slice aufnehmen kann.

TPUs können verwendet werden, um einen Job entweder auf einem einzelnen oder in mehreren Segmenten auszuführen. Weitere Informationen finden Sie in der Einführung in Multislice.

Ausfallsicherheit von Cloud TPU ICI

Die ICI-Resilienz verbessert die Fehlertoleranz von optischen Verbindungen und optischen Schaltungsschaltern (OCS), die TPUs zwischen Cubes verbinden. (ICI-Verbindungen innerhalb eines Cubes verwenden Kupferverbindungen, die nicht betroffen sind.) Dank der ICI-Resilienz können ICI-Verbindungen um OCS- und optische ICI-Fehler weitergeleitet werden. Dadurch wird die Planungsverfügbarkeit von TPU-Slices verbessert, aber die ICI-Leistung wird vorübergehend beeinträchtigt.

Ähnlich wie bei Cloud TPU v4 ist die ICI-Robustheit standardmäßig für v5p-Slices aktiviert, die mindestens einen Cube haben:

- v5p-128 beim Angeben des Aclerator-Typs

- 4x4x4 beim Angeben der Beschleunigerkonfiguration

Ressource in der Warteschlange

Eine Darstellung von TPU-Ressourcen, die zum Einreihen und Verwalten einer Anfrage für eine TPU-Umgebung mit einem oder mehreren Segmenten verwendet wird. Weitere Informationen finden Sie im Nutzerhandbuch für Ressourcen in der Warteschlange.

Bereitstellung

Bereitstellung ist der Prozess der Bereitstellung eines trainierten Modells für maschinelles Lernen in einer Produktionsumgebung, in dem damit Vorhersagen oder Entscheidungen getroffen werden können. Latenz und Verfügbarkeit auf Dienstebene sind für die Bereitstellung wichtig.

Ein Host und mehrere Hosts

Ein TPU-Host ist eine VM, die auf einem physischen Computer ausgeführt wird, der mit TPU-Hardware verbunden ist. TPU-Arbeitslasten können einen oder mehrere Hosts verwenden.

Eine Arbeitslast mit einem einzelnen Host ist auf eine TPU-VM beschränkt. Eine Arbeitslast mit mehreren Hosts verteilt das Training auf mehrere TPU-VMs.

Slices

Ein Pod-Slice ist eine Sammlung von Chips, die sich alle im selben TPU-Pod befinden und über Hochgeschwindigkeits-Inter-Chip-Interconnect-Verbindungen (ICI) verbunden sind. Segmente werden je nach TPU-Version als Chips oder TensorCores beschrieben.

Chipform und Chiptopologie beziehen sich ebenfalls auf Scheibenformen.

SparseCore

v5p enthält vier SparseCores pro Chip. Dies sind Dataflow-Prozessoren, die Modelle beschleunigen, die auf Einbettungen in Empfehlungsmodellen basieren.

TPU-Pod

Ein TPU-Pod ist eine zusammenhängende Gruppe von TPUs, die über ein spezialisiertes Netzwerk gruppiert sind. Die Anzahl der TPU-Chips in einem TPU-Pod hängt von der TPU-Version ab.

TPU-VM oder TPU-Worker

Eine virtuelle Maschine, auf der Linux ausgeführt wird und die Zugriff auf die zugrunde liegenden TPUs hat. Eine TPU-VM wird auch als Worker bezeichnet.

TensorCores

TPU-Chips haben einen oder zwei TensorCores, um die Matrixmultiplikation auszuführen. Weitere Informationen zu TensorCores finden Sie in diesem ACM-Artikel.

Worker

Siehe TPU-VM.

TPU-Versionen

Die genaue Architektur eines TPU-Chips hängt von der verwendeten TPU-Version ab. Jede TPU-Version unterstützt auch unterschiedliche Segmentgrößen und Konfigurationen. Weitere Informationen zur Systemarchitektur und den unterstützten Konfigurationen finden Sie auf den folgenden Seiten:

TPU-Architekturen

Es gibt zwei TPU-Architekturen, die beschreiben, wie eine VM physisch mit dem TPU-Gerät verbunden ist: ein TPU-Knoten und eine TPU-VM. Der TPU-Knoten war die ursprüngliche TPU-Architektur für die TPU-Versionen v2 und v3. Mit v4 wurde die TPU-VM zur Standardarchitektur, aber beide Architekturen wurden unterstützt. Die TPU-Knotenarchitektur wurde verworfen und nur die TPU-VM wird unterstützt. Wenn Sie TPU-Knoten verwenden, finden Sie unter Von TPU-Knoten zur TPU-VM-Architektur wechseln Informationen zur Umwandlung von der TPU-Knoten- zur TPU-VM-Architektur.

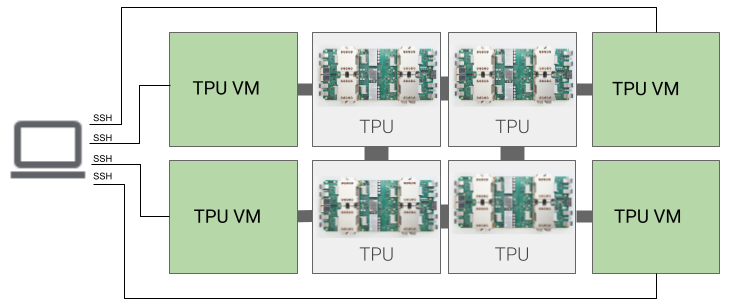

TPU-VM-Architektur

Mit der TPU-VM-Architektur können Sie über SSH eine direkte Verbindung zur VM herstellen, die physisch mit dem TPU-Gerät verbunden ist. Sie haben Root-Zugriff auf die VM, sodass Sie beliebigen Code ausführen können. Sie haben die Möglichkeit, auf Compiler- und Laufzeit-Debug-Logs sowie auf Fehlermeldungen zuzugreifen.

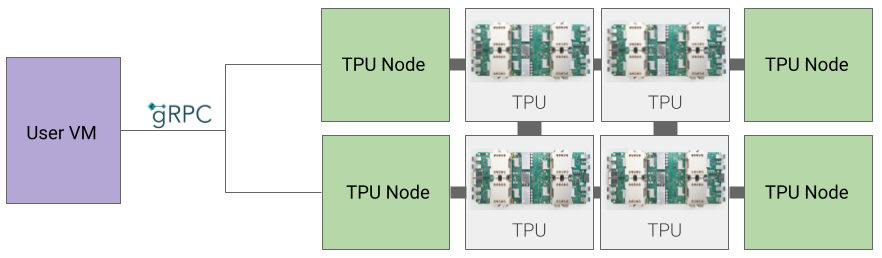

TPU-Knotenarchitektur

Die TPU-Knotenarchitektur besteht aus einer Nutzer-VM, die über gRPC mit dem TPU-Host kommuniziert. Bei Verwendung dieser Architektur können Sie nicht direkt auf den TPU-Host zugreifen, was das Debuggen von Trainings- und TPU-Fehlern erschwert.

Vom TPU-Knoten zur TPU-VM-Architektur wechseln

Wenn Sie TPUs mit der TPU-Knotenarchitektur haben, führen Sie die folgenden Schritte aus, um sie als TPU-VMs zu identifizieren, zu löschen und neu bereitzustellen.

Rufen Sie die TPU-Seite auf:

- Suchen Sie Ihre TPU und ihre Architektur unter der Überschrift Architektur. Wenn die Architektur „TPU-VM“ ist, müssen Sie nichts unternehmen. Wenn die Architektur ein „TPU-Knoten“ ist, müssen Sie die TPU löschen und neu bereitstellen.

Löschen Sie die TPU und stellen Sie sie neu bereit.

Eine Anleitung zum Löschen und erneuten Bereitstellen von TPUs finden Sie unter TPUs verwalten.