Arsitektur TPU

Tensor Processing Unit (TPU) adalah sirkuit terintegrasi khusus aplikasi (ASIC) yang dirancang oleh Google untuk mempercepat beban kerja machine learning. Cloud TPU adalah Google Cloud layanan yang menyediakan TPU sebagai resource yang skalabel.

TPU dirancang untuk melakukan operasi matriks dengan cepat sehingga cocok untuk beban kerja machine learning. Anda dapat menjalankan beban kerja machine learning di TPU menggunakan framework seperti Pytorch dan JAX.

Bagaimana cara kerja TPU?

Untuk memahami cara kerja TPU, sebaiknya pahami cara akselerator lain mengatasi tantangan komputasi dalam melatih model ML.

Cara kerja CPU

CPU adalah prosesor serbaguna berdasarkan arsitektur von Neumann. Artinya, CPU bekerja dengan software dan memori seperti ini:

Manfaat terbesar CPU adalah fleksibilitasnya. Anda dapat memuat jenis software apa pun di CPU untuk berbagai jenis aplikasi. Misalnya, Anda dapat menggunakan CPU untuk pemrosesan kata di PC, mengontrol mesin roket, menjalankan transaksi bank, atau mengklasifikasikan gambar dengan jaringan saraf.

CPU memuat nilai dari memori, melakukan penghitungan pada nilai, dan menyimpan hasilnya kembali ke memori untuk setiap penghitungan. Akses memori lambat jika dibandingkan dengan kecepatan penghitungan dan dapat membatasi total throughput CPU. Hal ini sering disebut sebagai bottleneck von Neumann.

Cara kerja GPU

Untuk mendapatkan throughput yang lebih tinggi, GPU berisi ribuan Arithmetic Logic Unit (ALU) dalam satu prosesor. GPU modern biasanya berisi antara 2.500–5.000 ALU. Jumlah prosesor yang besar berarti Anda dapat menjalankan ribuan perkalian dan penambahan secara bersamaan.

Arsitektur GPU ini berfungsi dengan baik pada aplikasi dengan paralelisme besar, seperti operasi matriks dalam jaringan saraf. Faktanya, pada beban kerja pelatihan biasa untuk deep learning, GPU dapat memberikan throughput yang jauh lebih tinggi daripada CPU.

Namun, GPU masih merupakan prosesor serbaguna yang harus mendukung banyak aplikasi dan software yang berbeda. Oleh karena itu, GPU memiliki masalah yang sama dengan CPU. Untuk setiap penghitungan dalam ribuan ALU, GPU harus mengakses register atau memori bersama untuk membaca operand dan menyimpan hasil penghitungan perantara.

Cara kerja TPU

Google mendesain Cloud TPU sebagai prosesor matriks yang dikhususkan untuk workload jaringan neural. TPU tidak dapat menjalankan pengolah kata, mengontrol mesin roket, atau menjalankan transaksi bank, tetapi dapat menangani operasi matriks besar yang digunakan dalam jaringan neural dengan kecepatan tinggi.

Tugas utama untuk TPU adalah pemrosesan matriks, yang merupakan kombinasi operasi perkalian dan akumulasi. TPU berisi ribuan multiply-accumulator yang terhubung langsung satu sama lain untuk membentuk matriks fisik yang besar. Ini disebut arsitektur array sistolik. Cloud TPU v3, berisi dua array sistolik 128 x 128 ALU, pada satu prosesor.

Host TPU melakukan streaming data ke antrean infeed. TPU memuat data dari antrean infeed dan menyimpannya di memori HBM. Setelah komputasi selesai, TPU akan memuat hasilnya ke dalam antrean feed keluar. Host TPU kemudian membaca hasil dari antrean feed keluar dan menyimpannya di memori host.

Untuk melakukan operasi matriks, TPU memuat parameter dari memori HBM ke dalam Unit Perkalian Matriks (MXU).

Kemudian, TPU memuat data dari memori HBM. Saat setiap perkalian dieksekusi, hasilnya akan diteruskan ke penghitung perkalian berikutnya. Outputnya adalah jumlah semua hasil perkalian antara data dan parameter. Tidak ada akses memori yang diperlukan selama proses perkalian matriks.

Akibatnya, TPU dapat mencapai throughput komputasi tinggi pada penghitungan jaringan neural.

Arsitektur sistem TPU

Bagian berikut menjelaskan konsep utama sistem TPU. Untuk mengetahui informasi selengkapnya tentang istilah machine learning umum, lihat Glosarium Machine Learning.

Jika Anda baru menggunakan Cloud TPU, lihat halaman beranda dokumentasi TPU.

Chip TPU

Chip TPU berisi satu atau beberapa TensorCore. Jumlah TensorCore bergantung pada versi chip TPU. Setiap TensorCore terdiri dari satu atau beberapa unit perkalian matriks (MXU), unit vektor, dan unit skalar. Untuk informasi selengkapnya tentang TensorCore, lihat Superkomputer Khusus Domain untuk Melatih Jaringan Neural Dalam.

MXU terdiri dari 256 x 256 (TPU v6e) atau 128 x 128 (versi TPU sebelum v6e) multiply-accumulator dalam array sistolik. MXU menyediakan sebagian besar daya komputasi di TensorCore. Setiap MXU mampu melakukan 16K operasi perkalian-akumulasi per siklus. Semua perkalian menggunakan input bfloat16, tetapi semua akumulasi dilakukan dalam format angka FP32.

Unit vektor digunakan untuk komputasi umum seperti aktivasi dan softmax. Unit skalar digunakan untuk alur kontrol, menghitung alamat memori, dan operasi pemeliharaan lainnya.

Pod TPU

Pod TPU adalah kumpulan TPU yang berdekatan dan dikelompokkan bersama melalui jaringan khusus. Jumlah TPU chip dalam Pod TPU bergantung pada versi TPU.

Slice

Slice adalah kumpulan chip yang semuanya berada di dalam Pod TPU yang sama dan terhubung oleh interkoneksi antar-chip berkecepatan tinggi (ICI). Slice dijelaskan dalam hal chip atau TensorCore, bergantung pada versi TPU.

Bentuk chip dan topologi chip juga merujuk pada bentuk slice.

Multislice versus satu slice

Multislice adalah sekelompok slice, yang memperluas konektivitas TPU di luar koneksi interkoneksi antar-chip (ICI) dan memanfaatkan jaringan pusat data (DCN) untuk mengirim data di luar slice. Data dalam setiap slice masih ditransmisikan oleh ICI. Dengan menggunakan konektivitas hibrida ini, Multislice memungkinkan paralelisme di seluruh slice dan memungkinkan Anda menggunakan lebih banyak core TPU untuk satu tugas daripada yang dapat ditampung oleh satu slice.

TPU dapat digunakan untuk menjalankan tugas di satu slice atau beberapa slice. Lihat Pengantar multislice untuk detail selengkapnya.

Kubus TPU

Topologi 4x4x4 dari chip TPU yang saling terhubung. Hal ini hanya berlaku untuk topologi 3D (dimulai dengan TPU v4).

SparseCore

SparseCore adalah pemroses dataflow yang mempercepat model dengan mengandalkan embedding yang ada dalam model rekomendasi. v5p menyertakan empat SparseCore per chip, dan v6e menyertakan dua SparseCore per chip.

Resiliensi ICI Cloud TPU

Ketahanan ICI membantu meningkatkan toleransi error link optik dan optical circuit switch (OCS) yang menghubungkan TPU di antara kubus. (Koneksi ICI dalam kubus menggunakan link tembaga yang tidak terpengaruh). Ketahanan ICI memungkinkan koneksi ICI dirutekan di sekitar OCS dan kerusakan ICI optik. Hasilnya, hal ini meningkatkan ketersediaan penjadwalan slice TPU, dengan mengorbankan degradasi sementara pada performa ICI.

Untuk Cloud TPU v4 dan v5p, ketahanan ICI diaktifkan secara default untuk slice yang berukuran satu kubus atau lebih besar, misalnya:

- v5p-128 saat menentukan jenis akselerator

- 4x4x4 saat menentukan konfigurasi akselerator

Versi TPU

Arsitektur chip TPU yang tepat bergantung pada versi TPU yang Anda gunakan. Setiap versi TPU juga mendukung ukuran dan konfigurasi slice yang berbeda. Untuk mengetahui informasi selengkapnya tentang arsitektur sistem dan konfigurasi yang didukung, lihat halaman berikut:

Arsitektur cloud TPU

Google Cloud menyediakan TPU sebagai resource komputasi melalui VM TPU. Anda dapat langsung menggunakan VM TPU untuk workload atau menggunakannya melalui Google Kubernetes Engine atau Vertex AI. Bagian berikut menjelaskan komponen utama arsitektur cloud TPU.

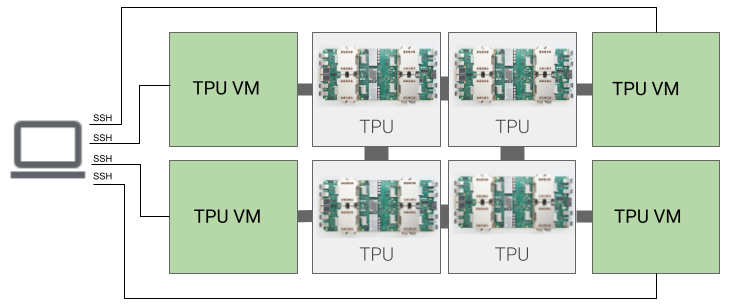

Arsitektur VM TPU

Arsitektur VM TPU memungkinkan Anda terhubung langsung ke VM yang terhubung secara fisik ke perangkat TPU menggunakan SSH. VM TPU, yang juga dikenal sebagai pekerja, adalah virtual machine yang menjalankan Linux dan memiliki akses ke TPU yang mendasarinya. Anda memiliki akses root ke VM, sehingga dapat menjalankan kode arbitrer. Anda dapat mengakses log debug compiler dan runtime serta pesan error.

Host tunggal, multi-host, dan sub-host

Host TPU adalah VM yang berjalan di komputer fisik yang terhubung ke hardware TPU. Workload TPU dapat menggunakan satu atau beberapa host.

Workload host tunggal dibatasi hingga satu VM TPU. Workload multi-host mendistribusikan pelatihan di beberapa VM TPU. Beban kerja sub-host tidak menggunakan semua chip di VM TPU.

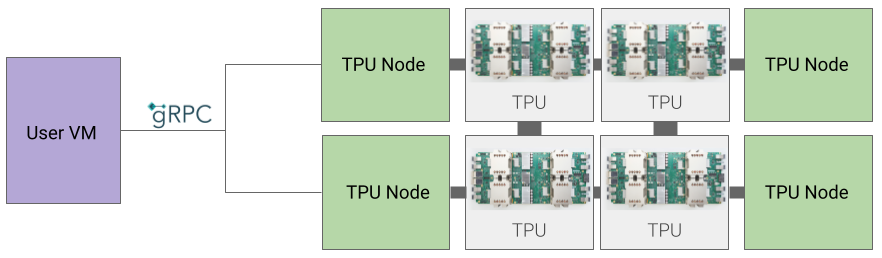

Arsitektur TPU Node (tidak digunakan lagi)

Arsitektur TPU Node terdiri dari VM pengguna yang berkomunikasi dengan host TPU melalui gRPC. Saat menggunakan arsitektur ini, Anda tidak dapat langsung mengakses Host TPU, sehingga sulit untuk men-debug error pelatihan dan TPU.

Beralih dari arsitektur TPU Node ke TPU VM

Jika Anda memiliki TPU yang menggunakan arsitektur TPU Node, gunakan langkah-langkah berikut untuk mengidentifikasi, menghapus, dan menyediakan ulang TPU sebagai VM TPU.

Buka halaman TPU:

Temukan TPU dan arsitekturnya di bagian judul Architecture. Jika arsitekturnya adalah "TPU VM", Anda tidak perlu melakukan tindakan apa pun. Jika arsitekturnya adalah "TPU Node", Anda perlu menghapus dan menyediakan ulang TPU.

Hapus dan sediakan ulang TPU.

Lihat Mengelola TPU untuk mengetahui petunjuk tentang cara menghapus dan menyediakan ulang TPU.