TPU v5e

이 문서에서는 Cloud TPU v5e의 아키텍처와 지원되는 구성을 설명합니다.

TPU v5e는 단일 및 멀티 호스트 학습과 단일 호스트 추론을 지원합니다. Sax를 사용하여 멀티 호스트 추론이 지원됩니다. 자세한 내용은 Cloud TPU 추론을 참고하세요.

시스템 아키텍처

각 v5e 칩에는 TensorCore 하나가 포함됩니다. 각 TensorCore에는 4개의 행렬 곱셈 단위(MXU), 벡터 단위, 스칼라 단위가 있습니다.

다음 다이어그램은 TPU v5e 칩을 보여줍니다.

다음 표에서는 v5e의 주요 칩 사양과 해당 값을 보여줍니다.

| 주요 칩 사양 | v5e 값 |

|---|---|

| 칩당 최고 컴퓨팅(bf16) | 197TFLOPs |

| HBM2 용량 및 대역폭 | 16GB, 819GBps |

| Interchip Interconnect BW | 1600Gbps |

다음 표는 v5e의 포드 사양 및 값을 보여줍니다.

| 주요 포드 사양 | v5e 값 |

|---|---|

| TPU Pod 크기 | 칩 256개 |

| 상호 연결 토폴로지 | 2D 토러스 |

| 포드당 최고 컴퓨팅 | 100페타옵스(Int8) |

| 포드당 올리듀스 대역폭 | 51.2TB/초 |

| 포드당 바이섹션 대역폭 | 1.6TB/초 |

| 포드당 데이터 센터 네트워크 대역폭 | 6.4Tbps |

구성

Cloud TPU v5e는 학습 및 추론(제공) 제품 조합입니다. 학습 환경과 추론 환경을 구분하려면 TPU API에 AcceleratorType 매개변수를 사용하거나 Google Kubernetes Engine(GKE) 노드 풀을 만들 때 --machine-type 플래그를 사용하세요.

학습 작업은 처리량과 가용성에 최적화되어 있고 서빙 작업은 지연 시간에 최적화되어 있습니다. 서빙용으로 프로비저닝된 TPU에서는 학습 작업의 가용성이 낮을 수 있고, 학습용으로 프로비저닝된 TPU에서 서빙 작업을 실행하면 지연 시간이 길어질 수 있습니다.

AcceleratorType을 사용하여 사용할 TensorCore 수를 지정합니다.

gcloud CLI 또는 Google Cloud 콘솔을 사용하여 TPU를 만들 때 AcceleratorType을 지정합니다. AcceleratorType에 지정하는 값은 v$VERSION_NUMBER-$CHIP_COUNT 형식의 문자열입니다.

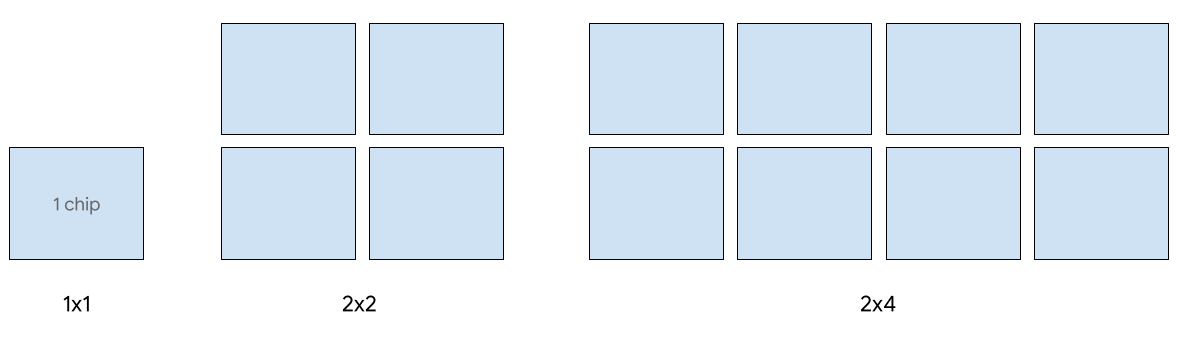

v5e에는 다음 2D 슬라이스 형태가 지원됩니다.

| 토폴로지 | TPU 칩 수 | 호스트 수 |

|---|---|---|

| 1x1 | 1 | 1/8 |

| 2x2 | 4 | 1/2 |

| 2x4 | 8 | 1 |

| 4x4 | 16 | 2 |

| 4x8 | 32 | 4 |

| 8x8 | 64 | 8 |

| 8x16 | 128 | 16 |

| 16x16 | 256 | 32 |

VM 유형

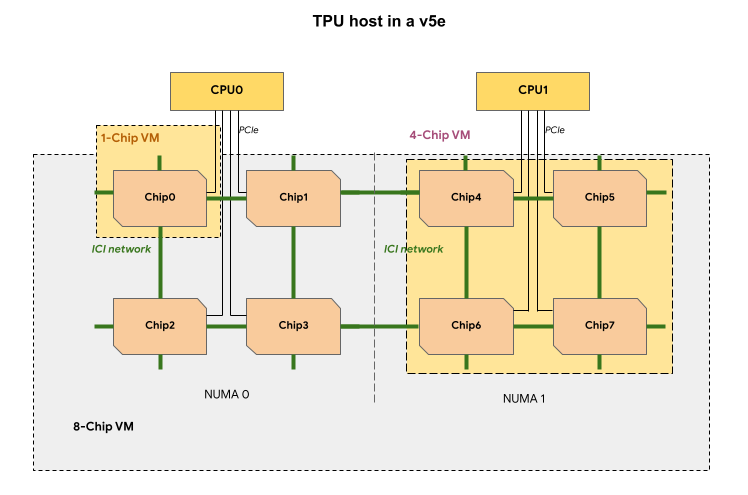

v5e TPU 슬라이스의 각 TPU VM에는 1개, 4개 또는 8개의 칩이 포함되어 있습니다. 칩이 4개인 작은 슬라이스에서는 모든 TPU 칩이 동일한 비균일 메모리 액세스(NUMA) 노드를 공유합니다.

칩이 8개인 v5e TPU VM의 경우 NUMA 파티션 내에서 CPU-TPU 통신이 더 효율적입니다. 예를 들어 다음 그림에서는 CPU0-Chip0 통신이 CPU0-Chip4 통신보다 빠릅니다.

다음은 TPU v5e VM 유형을 비교한 표입니다.

| VM 유형 | 머신 유형(GKE API) | VM당 vCPU 수 | VM당 RAM(GB) | VM당 NUMA 노드 수 |

|---|---|---|---|---|

| 1칩 VM | ct5lp-hightpu-1t |

24 | 48 | 1 |

| 4칩 VM | ct5lp-hightpu-4t |

112 | 192 | 1 |

| 8칩 VM | ct5lp-hightpu-8t |

224 | 384 | 2 |

서빙을 위한 Cloud TPU v5e 유형

단일 호스트 서빙은 최대 8개의 v5e 칩에 지원됩니다. 1x1, 2x2, 2x4 슬라이스 구성이 지원됩니다. 각 슬라이스에는 칩이 1개, 4개, 8개 있습니다.

서빙 작업용으로 TPU를 프로비저닝하려면 CLI 또는 API TPU 만들기 요청에 다음 가속기 유형 중 하나를 사용합니다.

| AcceleratorType(TPU API) | 머신 유형(GKE API) |

|---|---|

v5litepod-1 |

ct5lp-hightpu-1t |

v5litepod-4 |

ct5lp-hightpu-4t |

v5litepod-8 |

ct5lp-hightpu-8t |

다음 명령어는 서비스를 위해 8개의 v5e 칩이 포함된 v5e TPU 슬라이스를 만듭니다.

$ gcloud compute tpus tpu-vm create your-tpu-name \ --zone=us-central1-a \ --accelerator-type=v5litepod-8 \ --version=v2-alpha-tpuv5-lite

TPU 관리에 대한 자세한 내용은 TPU 관리를 참고하세요. Cloud TPU의 시스템 아키텍처에 대한 자세한 내용은 시스템 아키텍처를 참고하세요.

8개를 초과하는 v5e 칩에 대한 서빙(멀티 호스트 서빙이라고도 함)은 Sax를 사용하여 지원됩니다. 자세한 내용은 Cloud TPU 추론을 참고하세요.

학습용 Cloud TPU v5e 유형

학습은 최대 256개의 칩에 대해 지원됩니다.

v5e 학습 작업용으로 TPU를 프로비저닝하려면 CLI 또는 API TPU 만들기 요청에 다음 가속기 유형 중 하나를 사용합니다.

| AcceleratorType(TPU API) | 머신 유형(GKE API) | 토폴로지 |

|---|---|---|

v5litepod-16 |

ct5lp-hightpu-4t |

4x4 |

v5litepod-32 |

ct5lp-hightpu-4t |

4x8 |

v5litepod-64 |

ct5lp-hightpu-4t |

8x8 |

v5litepod-128 |

ct5lp-hightpu-4t |

8x16 |

v5litepod-256 |

ct5lp-hightpu-4t |

16x16 |

다음 명령어는 학습을 위해 256개의 v5e 칩이 포함된 v5e TPU 슬라이스를 만듭니다.

$ gcloud compute tpus tpu-vm create your-tpu-name \ --zone=us-east5-a \ --accelerator-type=v5litepod-256 \ --version=v2-alpha-tpuv5-lite

TPU 관리에 대한 자세한 내용은 TPU 관리를 참고하세요. Cloud TPU의 시스템 아키텍처에 대한 자세한 내용은 시스템 아키텍처를 참고하세요.